此项目工作可分为两大部分,即上下变频通道设计和功放测试系统的搭建。

(1)81~86 GHz上下变频通道设计

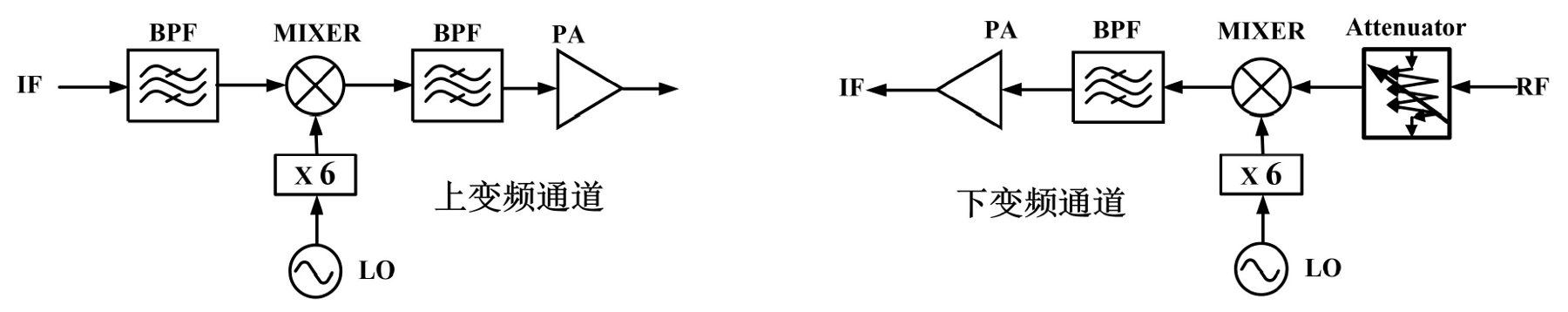

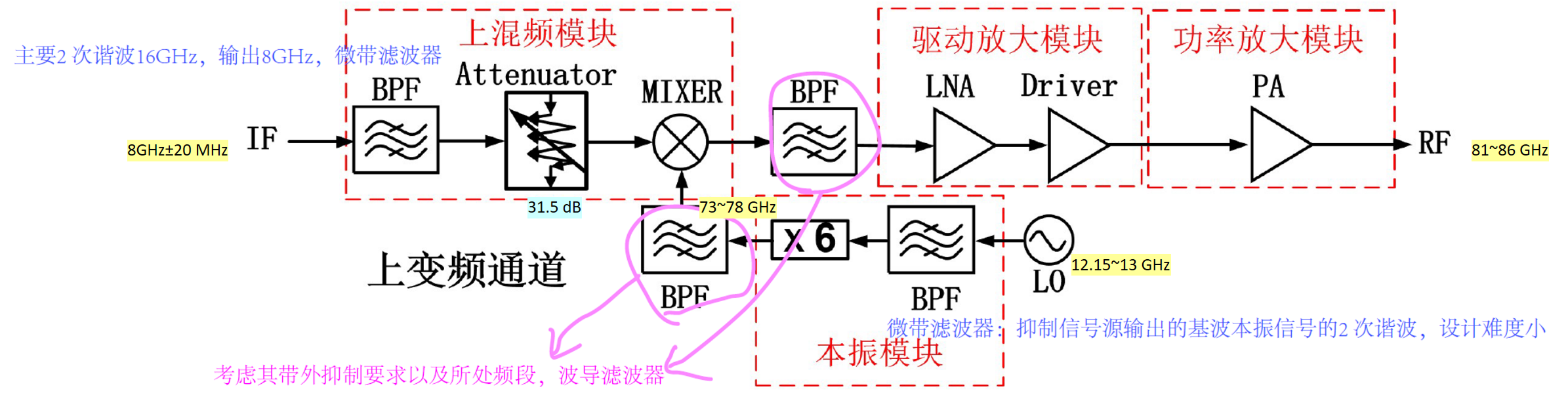

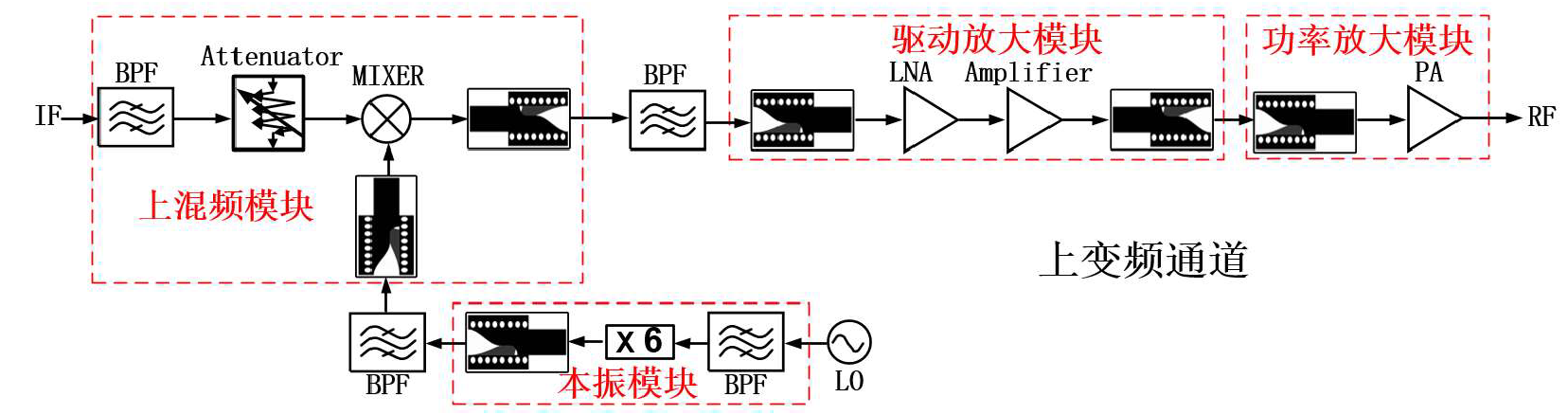

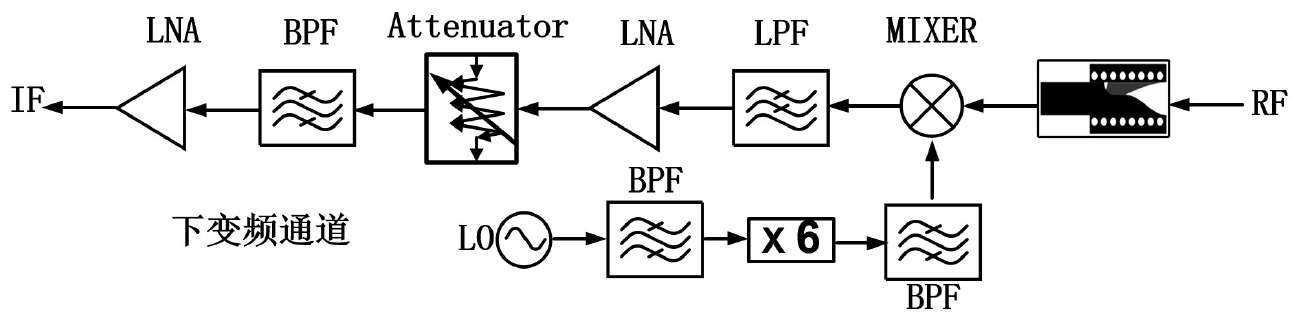

均采用一次变频的超外差结构,本振采用外部信号源供给。对上下变频通道采用模块化设计。上变频通道包含本振倍频模块、上混频模块、驱动放大模块以及功率放大模块,整个上变频通道可以提供超过30 dB 的可变增益,在81~86 GHz 频率范围内输出1 dB 压缩点大于27.2 dBm。下变频通道可以提供超过20 dB 增益,输出1 dB 压缩点大于16 dBm,中频带宽大于200 MHz。

针对81~86 GHz频段功率放大器的典型指标“小信号增益:18dB,功率增益13dB,饱和输出功率34dBm”,设置如下变频通道指标:

| “上变频通道”技术指标 | 要求 |

|---|---|

| 中频频率 | 8GHz±20MHz |

| 本振频率 | 12.15~13 GHz |

| 输出频率 | 81~86 GHz |

| 输入功率 | -5~-9 dBm |

| 输出功率 | ≥22 dBm |

| 输出P1dB | ≥25 dBm |

| 本振泄露抑制 | ≥30 dBc |

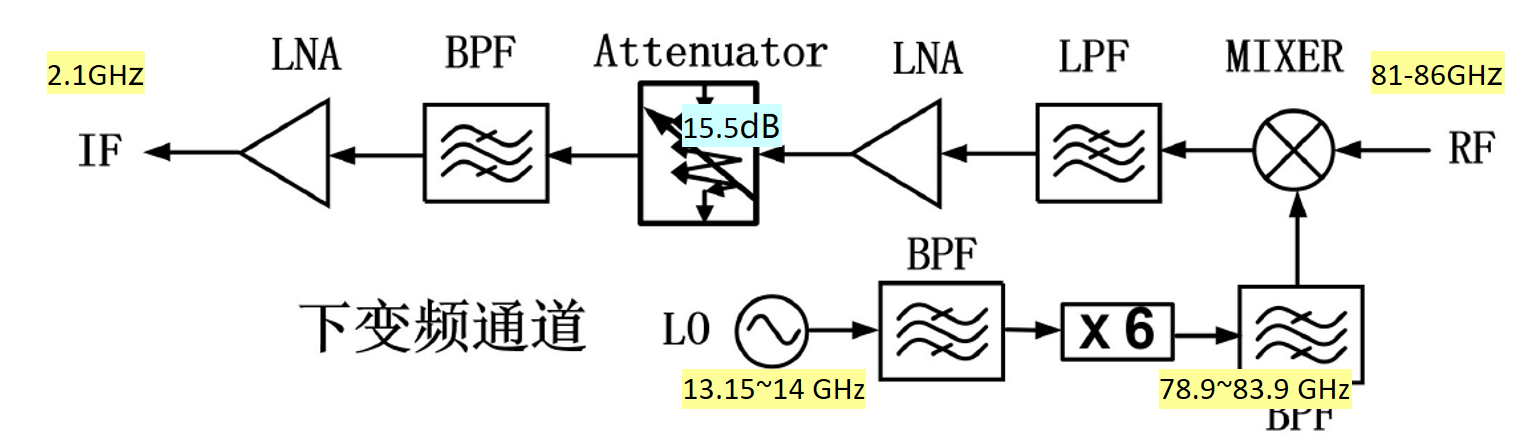

| “下变频通道”技术指标 | 要求 |

|---|---|

| 输入频率 | 81~86 GHz |

| 输入功率 | ≤-10 dBm |

| 输入本振频率 | 13.15~14 GHz |

| 输出中心频率 | 2.1 GHz |

| 输出功率 | 1~6 dBm |

| 输出P1dB | ≥15 dBm |

| 中频带宽 | ≥200 MHz |

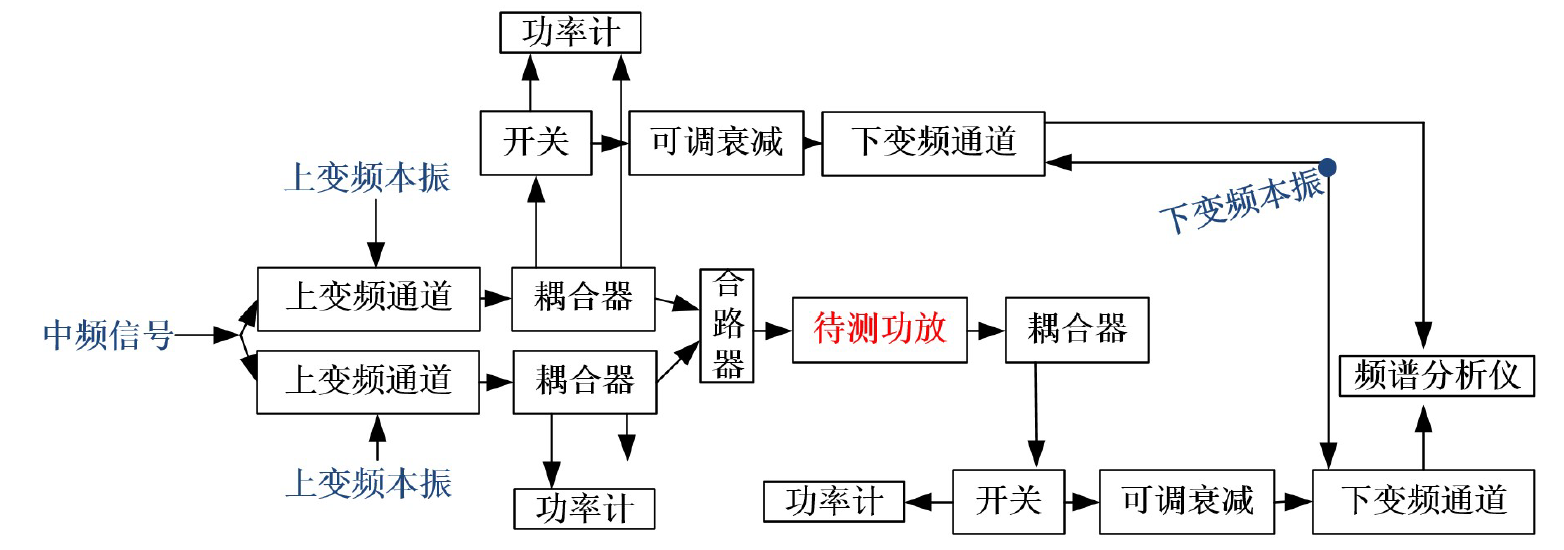

(2)功放测试系统搭建

利用上变频通道为待测件提供测试信号;利用下变频通道将待测件的输出信号下变频至信号分析仪,用于频谱分析和EVM分析。该前端可为待测件提供超过25dBm 的测试信号,用40MHz 的QPSK 信号和250 MHz 的64QAM 调制信号验证了该前端的线性度。综合来看,该前端可完成待测件的大小信号增益、输入输出1dB 压缩点、饱和输出功率、输入驻波、输出三阶交截点OIP3以及EVM 的测试。

一、上下变频通道设计

(一)方案设计

1、上变频通道

上变频通道增益分配全在毫米波频段。若在中频阶段就分配较大增益,会使链路的1 dB 压缩点受混频器限制。由于将增益过多分配至毫米波频段,容易造成自激现象,因此将功率增益链路分为两个模块,方便调试过程中做端口匹配。

上变频本振频率的范围为73 GHz至78 GHz ,设计的滤波器应该对离81~86 GHz 信号最近的78 GHz 进行抑制,另外还需要考虑到对输出信号的杂散抑制,特别需要考虑三阶交调(LO±2*IF)信号。

2、下变频通道

本振泄露距离中频信号远,中频滤波器可以将其完全滤除,因此本振滤波器可使用阶数较低微带滤波器,使得整个下变频通道可集成为一个模块,大大减小了尺寸。

混频后,先利低通滤波器将本振泄露、射频泄露以及高频的交调分量滤除,再用中心频率为2.1 GHz 的带通滤波器将信号滤出。增益完全分配至中频频段,大降低成本,并通过数控衰减器调整中频输出功率,方便仪器测量。

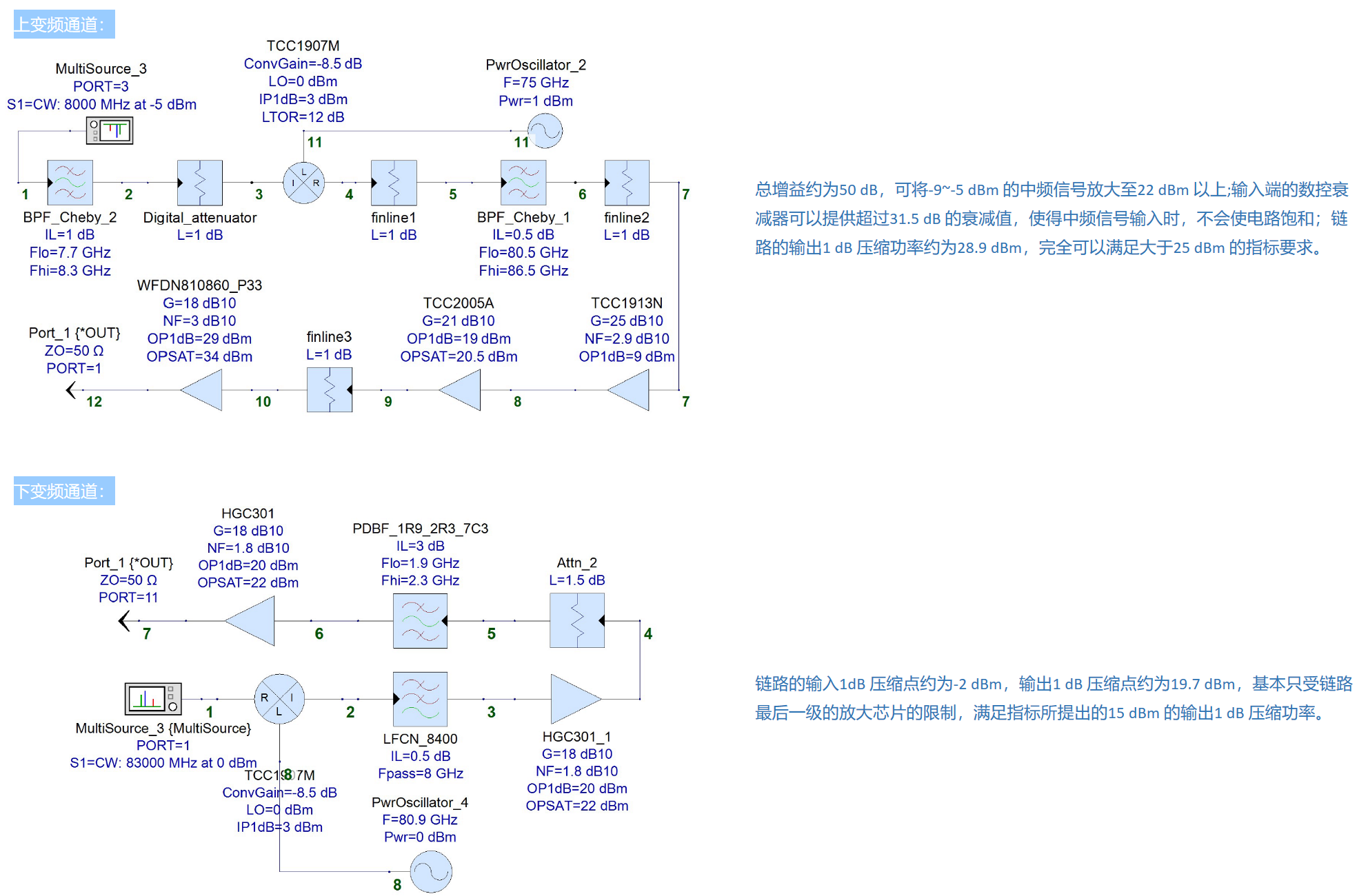

(二)利用Systemvue进行方案仿真

链路模型包含了对极鳍线过渡结构,考虑过渡结构带来的损耗,在模型中用固定的衰减器表示。应保证完成指标的同时,留有调整的余量。链路节点增益,输入输出功率仿真(可看P1dB)如下图。

链路1dB压缩点:从后往前倒推输入功率,看哪一级最先压缩。最终链路的P1dB,就是最小的那个输入功率对应的位置。

功放测试前端对线性度要求较高。输出1 dB压缩点只能从功率压缩的角度反应射频链路的线性度,用Systemvue 对整个上下变频通道的线性度进行仿真,搭建仿真电路包含基带信号发生电路和射频链路。

①首先设计基带信号:中心频率为8 GHz,带宽40 MHz,调制方式选择QPSK,基带信功率为设定为-5.84 dBm。仿真星座图清晰,EVM 约为0.7814%。

②将电路中的RF_LINK 控件指向上变频通道的电路。40Hz 带宽的QPSK 调制信号进行仿真,在通道输出功率为17.31 dBm (足够驱动功放至P1dB)时,链路的EVM 为0.8058%,在该功率输出下,上变频通道几乎对信号不产生恶化。

③将上下变频通道集成在一起,利用下变频通道的衰减器使输入下变频通道的功率小于-10 dBm。能在功率谱图中看到,信号已经被变频到2.1 GHz,带宽40 MHz,在4.627 dBm 输出的情况下,星座图分布清晰可见,EVM 为0.8544%。

按上述方案设计,可以保证通道EVM 良好。当应用在功放测试前端时,对测试结果的影响可以忽略不计。

(三)无源电路设计

1、波导滤波器

波导滤波器对加工精度要求高,加工成本高,但其优点是设计简单,功率容量大,Q值高插入损耗小,在保证加工精度的情况下能实现插入损耗<1 dB。上变频通道中两波导滤波器的设计使用散射参数法,通过插入电感膜片来实现,并加入R=0.3mm 的倒角,以减小仿真误差。

| 波导滤波器 | 性能设计 |

|---|---|

| 抑制混频杂散的81~86 GHz滤波器 | 主要滤除LO,LO+2IF,LO-IF |

| 73-78 GHz 的本振滤波器 | 滤除6倍频后的谐波,主要为5次,7次谐波。 |

注意:上变频本振滤波器中,7次谐波(85.05-91 GHz)有部分包含在81-86 GHz 频带内,经混频器泄露之后,后面的滤波器无法滤除,需要在混频器前尽可能抑制。

2、微带滤波器及其转换电路

一些频率较低,指标要求较低的滤波器是基于微带传输线的。设计简单,加工成本较低,且相较于波导滤波器有更小的体积。

| 微带无源电路 | 性能设计 |

|---|---|

| 12.15~14 GHz 滤波器 | 抑制频率源的二次谐波,同时用于上下变频通道的基波本振滤波。 |

| 8 GHz 滤波器设计 | 保证频率源提供的8GHz中频频谱纯净,同时对二次谐波有抑制。 |

| 微带-波导过渡结构 | 使用鳍线结构,其具有插入损耗低、回波损耗大、频带宽和利于模块集成的优点。 |

(四)电路实现及测试结果

1、链路验证

将设计的无源电路S参数导入ADS进行仿真验证:上变频通道输出81 GHz 信号时,信号功率和基波本振的七次谐波之间相差约62 dBc,当减小输出信号功率为0 dBm 时,仍可以保证对本振泄露的抑制超过40 dBc,满足对本振泄露抑制大于30 dBc 的指标要求。另外,混频后的三阶交调分量89 GHz 和78GHz 都被抑制在100 dBc 以上。将上下变频通道级联,输出中频为2.1 GHz,整个链路输出频谱纯净,在输出大于0 dBm 的情况下对杂散抑制超过100 dBc。

2、上变频通道

(1)本振倍频模块:10 dBm、12.15-13 GHz输入时,所使用的六倍频器输出约14dBm,到达混频器的信号大小在超过10 dBm,而该混频器的本振驱动功率推荐值为0至3 dBm,本振信号过大会导致本振泄露过大。为了保证输出频谱的纯净度,在倍频模块输出端添加了9 dB 的固定衰减器。本振倍频模块输出经过滤波及鳍线后,到达到达混频器的信号大小在0~3 dBm 之间。

(2)上混频模块:实测的变频损耗约增大了10 dB,发现是混频器芯片仅能用于下变频,将其应用于上变频时,变频损耗会增大,但该芯片的变频损耗在带内平坦度不超过± 1dB,且由于方案设计保证链路增益有富余,因此仍保持设计不变。

(3)驱动放大模块:为消除级放大器级联可能带来的自激现象,在两个放大器芯片之间添加了吸波材料。

(4)功放模块及上变频通道测试:功放模块功耗较大,腔体设计散热齿帮助散热,整个通道固定在铝制金属散热板上,另有统一的供电电路板装配在金属板上。输出信号通过功率计对信号大小进行测试。自研功放模块输出1 dB 压缩点随频率升高下降较为明显,由于上变频通道要应用于功放测试前端,要级联其他器件,会带来额外损耗,降低输出1 dB 压缩点,从而无法满足大于25 dBm 的要求。采购同芯片型号的功率放大模块替换自研功放模块。替换后,上变频通道输出1 dB 压缩点在个频段均大于27 dB,G>32.2 dB 且增益平坦度优于±1.5 dB,可以保证输入功率在-9~-5 dBm 时仍然能使输出大于指标要求的22 dBm。在测试输入输出曲线时,将中频信号关闭,可以用功率计对本振泄露功率进行测试,测试结果显示可以保证在各频点的本质抑制均大于33 dBc。

3、下变频通道

下变频通道的增益在20-21 dB 之间,增益平坦度优于±0.5 dB,输出1 dB 压缩点大于17dBm,完全可以保证输入信号小于-10 dBm 时,输出信号功率范围为1~6 dBm。该通道的3 dB 中频带宽大于500 MHz,完全满足设计需求。

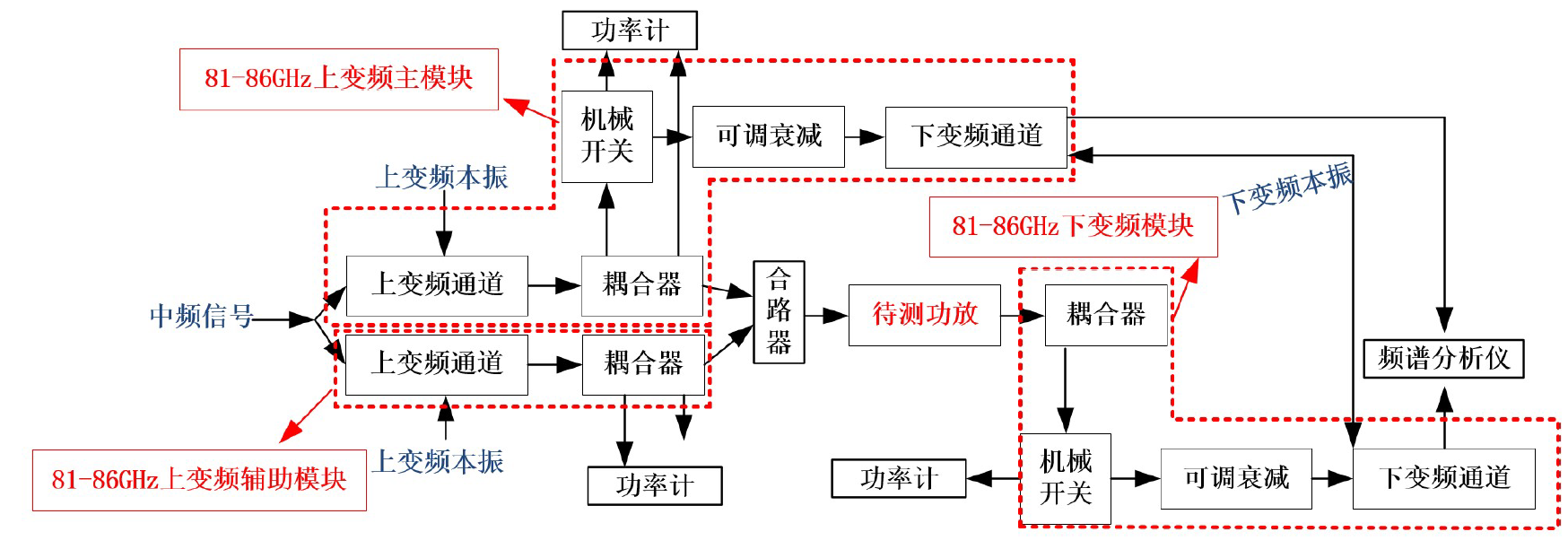

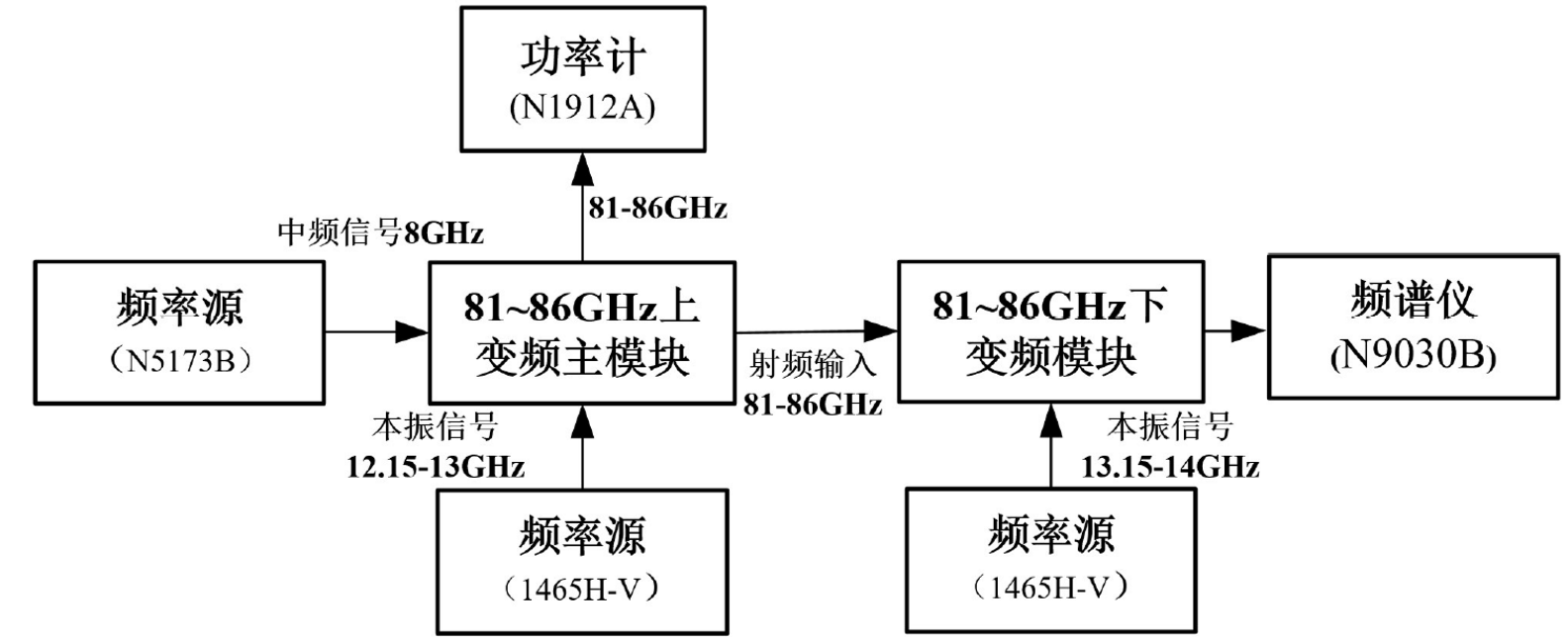

二、测试前端设计

上下变频通道所需的本振信号和中频调制信号分别用外部的频率源和矢量信号发生器提供 ;输出用频谱分析仪或信号分析仪进行测量。

(一)测试系统配置

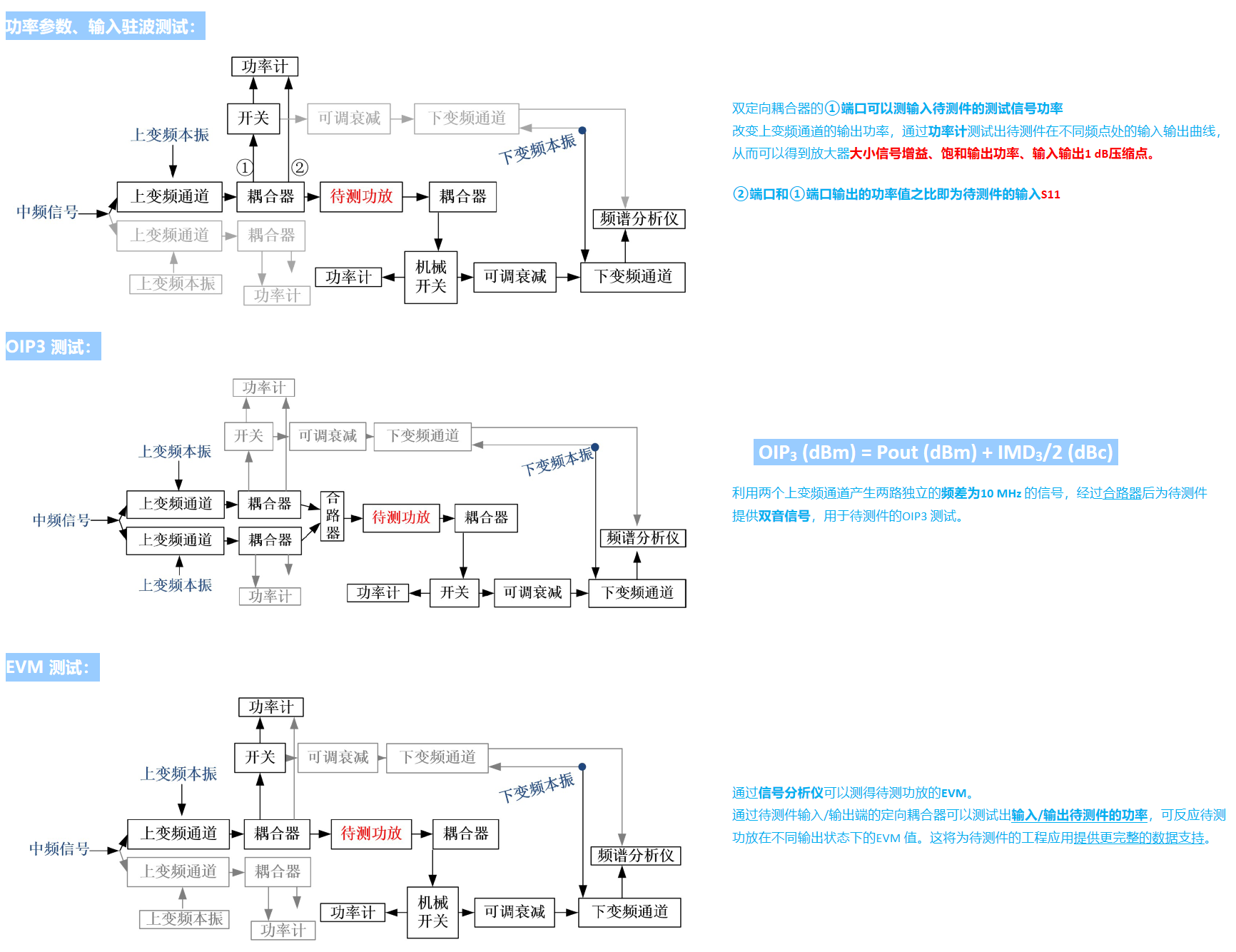

按以下配置分别进行①功率参数、输入驻波,②OIP3,③EVM的测试。

(二)方案实现

1、标准器件设计选型

(1)机械波导开关:一公共端两选通端,两路插损均<1.4dB,回波损耗均>12.5dB。

(2)机械衰减器:75-110 GHz,可调衰减量为0.5-30 dBm。

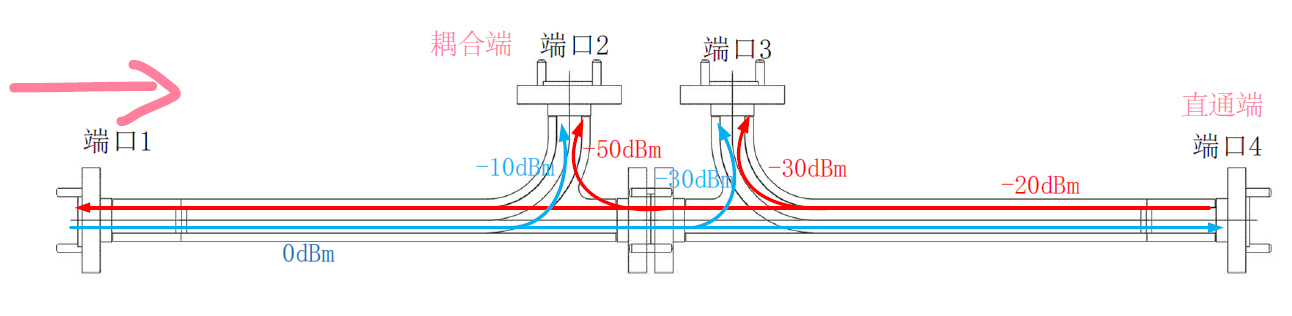

(3)定向耦合器:将两个三端口的定向耦合器组合成为一个双定向耦合器以进行驻波的测量。

对端口3 ,测试输入信号和反射信号大小相当,这将会极大的影响测试结果,因此耦合器的方向性是最为重要的参数。仿真验证得到方向性>30dB测得S11较精准。使用的定向耦合器技术协议为:耦合度为10 dB,方向性大于35 dB

2、合路器设计

采用波导3 dB 耦合电桥设计合路器,在隔离端填充劈尖型的吸波材料。实测各端口回波>10dB,隔离度>12 dB。

3、控制电路设计

上变频中的驱动放大模块放大器级联导致该模块极易自激,因此在驱动放大模块的输入输出端都添加隔离器,改善端口的匹配情况。为避免上电自激现象,对驱动放大模块的栅极电压进行调整,先提供-2V 的负压,使驱动放大模块稳定启动,然后将负压增大到-1.8V,这样可避免驱动放大模块自激。控制电路应用了负电保护技术,为芯片“先加负电,再加正电”,保证系统的稳定,防止芯片烧毁。

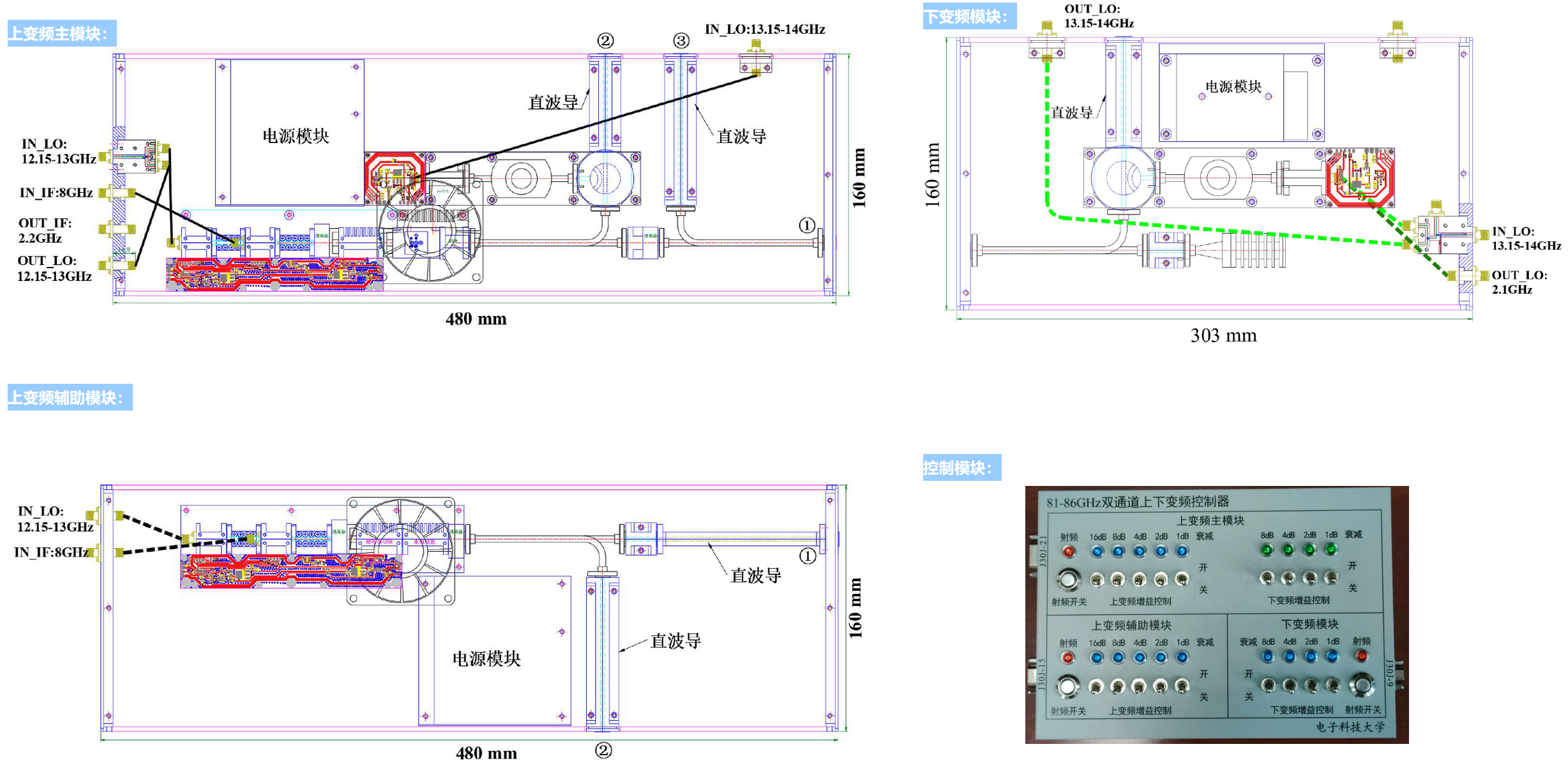

4、模块实现

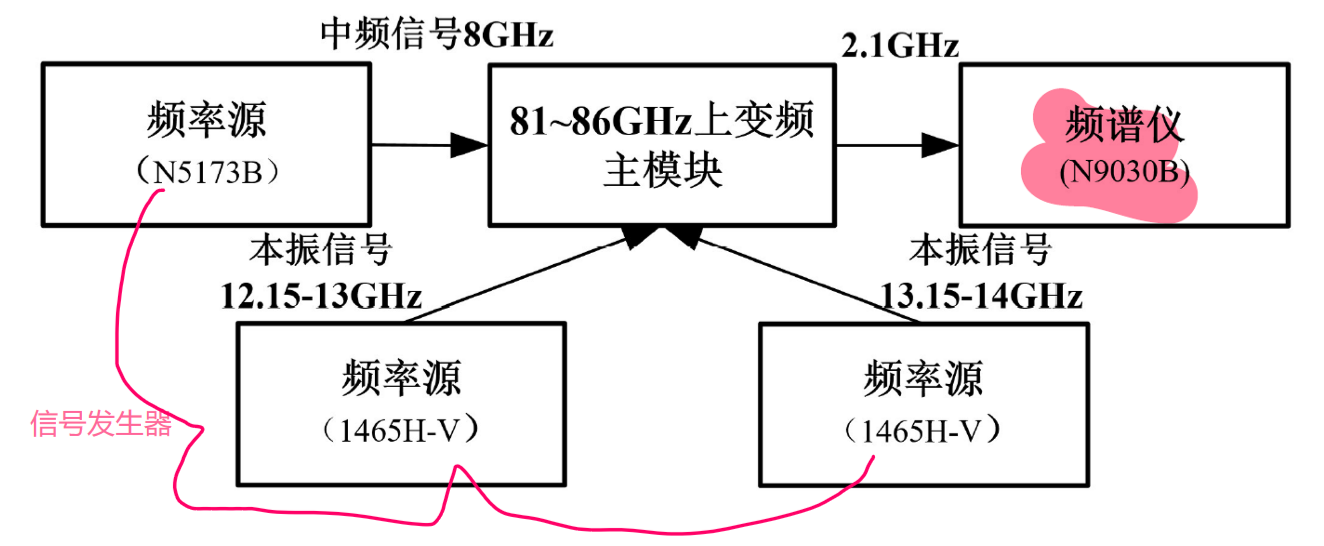

上变频主模块和辅模块使用相同的本振信号,上变频主模块的下变频本振和下变频模块使用相同的本振信号(sma接口), 以减少信号源的使用,降低测试成本。

控制模块通过J-30J 微矩形连接器与模块通信,通过拨码开关对各模块中的数控衰减器的衰减值进行控制,另外增加了射频控制开关,用于启动模块和关闭模块。

(三)测试

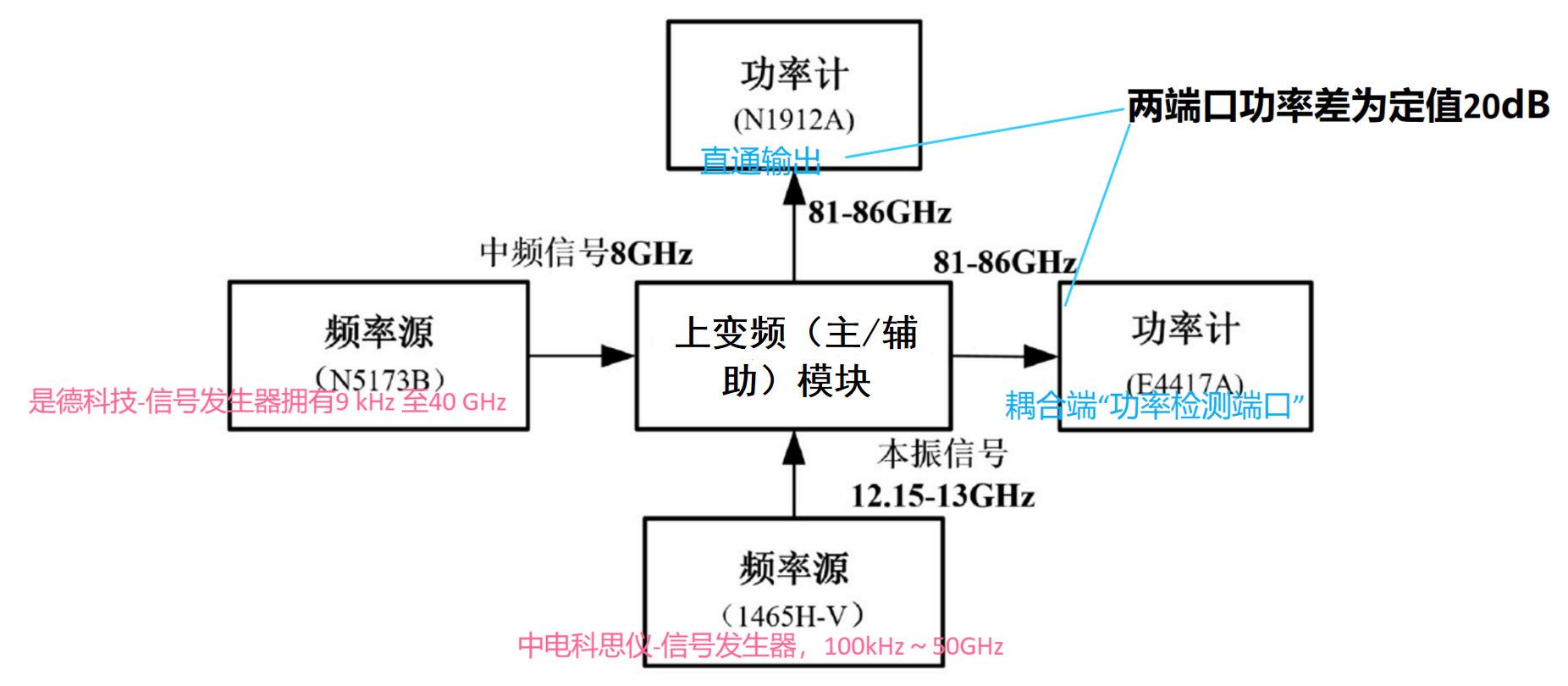

1、上变频通道测试

输出信号在81~86 GHz,超出现有频谱分析仪的测试频率范围,因此使用功率计测试其输出的功率值。

(1)上变频主模块中的上变频通道

设置数控衰减器不衰,逐渐增加中频输入功率,通过改变本振频率在输出端口每隔1 GHz 测试其输出1 dB压缩点以及对应的功率增益:输出P1 dB 均>26.1 dBm(满足指标>25 dBm);增益>28.7 dB (保证在输入信号的范围在-9~-5 dBm 时,输出功率>22 dBm要求)。在测试输入输出曲线时,将中频信号关闭,可以测试其本振泄露功率,由于受到功率计的测试下限的限制,无法测试出其准确的对本振抑制能力,但测试保证各频点本振抑制均>33 dBc,满足大于30 dBc 的指标要求。

(2)上变频辅助模块中的上变频通道

该模块的输出P1 dB >24.2 dBm,虽然小于指标25 dBm 的要求,但该模块主要用于测试待测件的三阶交调,所需的输出信号为单载波且输出功率小,因此对测试前端的性能没有影响。能保证在各频点的本振抑制均>33 dBc。

2、下变频通道测试

(1)上变频主模块中的下变频通道

从耦合端口测出输入下变频通道的功率大小,从而测出下变频通道的输出P1 dB>16.6dBm ,增益>15 dBm。通过改变输入中频信号的频率,将其设置为扫频输出,将频谱仪设置为maxhold 模式,从频谱仪上可以看出通道级联后输出中频的带宽及平坦度:测得中频带宽>200 MHz,带内的平坦度优于±0.5 dB。

(2)下变频模块中的下变频通道

下变频模块仅集成一个下变频通道,因此需要用上变频主模块为其提供测试信号,因此将两个模块级联后进行测试:

输出P1 dB 均>16.4 dBm,满足指标中大于15 dBm 的要求;中频带宽>200 MHz,平坦度优于±0.5 dB

3、EVM测试

测试前端的线性度有较高的要求,输出1 dB 压缩点并不能完全反应系统的线性度,对测试前端的EVM 进行测试。

将8GHz、-5~-9 dBm 的中频信号源输出设定为符号率(symbol rate)为40 MHz的QPSK 调制信号,通过改变上下变频的本振频率,每隔1 GHz 对测试前端的EVM进行测试。经测试,在上变频通道输出15 dBm 时(该输出功率足以推动待测模块的功率至其1 dB 压缩点),各频点的EVM均<2%。工信部对E波段的信道划分,单个信道>250 MHz,因此设置中频信号为250MHz的QAM调制信号。上变频输出信号大于15 dBm 的情况下,除86GHz 频点外,调制信号的恶化仅为2%左右。考虑是因为测试的频率为86±125 MHz时,超出上变频通道中的高线性放大器的工作频段(81-86 GHz),增益呈明显下降的趋势。

4、OIP3测试

上变频主/辅模块同时工作为待测功放提供双音信号,经待测件后利用下变频模块将输出信号下变频,从频谱仪可观察到三阶交调信号和基波信号。

对待测功放抽取83 GHz 这个频点进行测试验证:该待测功放在25 dBm 输出时,其IMD3=25 dBc,由公式计算出OIP3=37.5dBm。并对比在不同功率下测出的结果,可以验证测试及计算结果的一致性。

- 本文作者: Eva

- 本文链接: https://tingtingeva.github.io/2025/05/24/E波段功放测试系统/

- 版权声明: 本博客所有文章除特别声明外,均采用 MIT 许可协议。转载请注明出处!